12. Analog-to-digital converter (ADC)

12.1 ADC introduction

The 12-bit ADC is a successive approximation analog-to-digital converter. It has up to 19 multiplexed channels allowing it measure signals from 16 external and three internal sources. A/D conversion of the various channels can be performed in single, continuous, scan or discontinuous mode. The result of the ADC is stored in a left-aligned or right-aligned 16-bit data register.

The analog watchdog feature allows the application to detect if the input voltage goes outside the user-defined high or low thresholds.

The ADC input clock is generated from the PCLK2 clock divided by a prescaler (refer to Figure 12: Clock tree part 1 ).

12.2 ADC main features

- • 12-bit resolution

- • Interrupt generation at End of Conversion, End of Injected conversion and Analog watchdog event

- • Single and continuous conversion modes

- • Scan mode for automatic conversion of channel 0 to channel 'n'

- • Self-calibration

- • Data alignment with in-built data coherency

- • Channel by channel programmable sampling time

- • External trigger option for both regular and injected conversion

- • Discontinuous mode

- • ADC conversion time:

- – 1 µs at 56 MHz (1.17 µs at 72 MHz)

- • ADC supply requirement: 2.4 V to 3.6 V

- • ADC input range: \( V_{REF-} \leq V_{IN} \leq V_{REF+} \)

- • DMA request generation during regular channel conversion

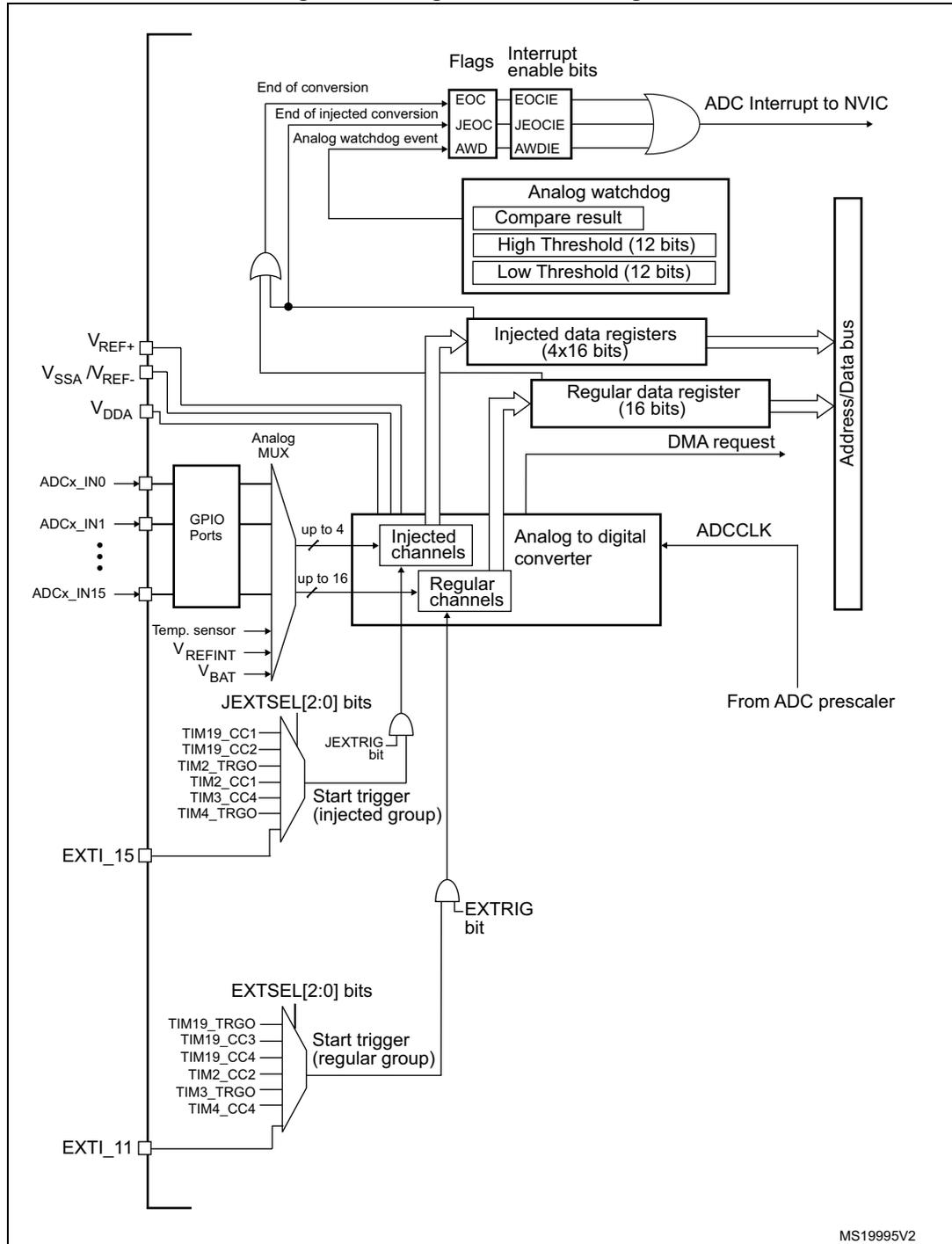

The block diagram of the ADC is shown in Figure 27 .

Note: \( V_{REF-} \) , if available (depending on package), must be tied to \( V_{SSA} \) .

12.3 ADC functional description

Figure 27 shows a single ADC block diagram and Table 30 gives the ADC pin description.

Figure 27. Single ADC block diagram

The diagram illustrates the internal architecture of the ADC. On the left, external pins are shown: \( V_{REF+} \) , \( V_{SSA} \) / \( V_{REF-} \) , \( V_{DDA} \) , \( ADCx\_IN0 \) , \( ADCx\_IN1 \) through \( ADCx\_IN15 \) , \( Temp. sensor \) , \( V_{REFINT} \) , and \( V_{BAT} \) . The \( ADCx\_IN \) pins connect to an Analog MUX via GPIO Ports . The MUX outputs are split into Injected channels (up to 4) and Regular channels (up to 16). These channels feed into the Analog to digital converter block. The converter is clocked by ADCCLK , which comes From ADC prescaler . The converter outputs data to Injected data registers (4x16 bits) and a Regular data register (16 bits) . These registers are connected to an Address/Data bus . A DMA request is generated from the Regular data register. The converter also produces flags: End of conversion (EOC) , End of injected conversion (JEOC) , and Analog watchdog event (AWD) . These flags are paired with Interrupt enable bits ( EOCIE , JEOCIE , AWDIE ) and combined in an OR gate to generate an ADC Interrupt to NVIC . An Analog watchdog block contains a Compare result , High Threshold (12 bits) , and Low Threshold (12 bits) . Start triggers are provided for both groups. The Start trigger (injected group) is controlled by JEXTSEL[2:0] bits and a JEXTRIG bit , with sources including TIM19_CC1 , TIM19_CC2 , TIM2_TRGO , TIM2_CC1 , TIM3_CC4 , TIM4_TRGO , and EXTI_15 . The Start trigger (regular group) is controlled by EXTSEL[2:0] bits and an EXTRIG bit , with sources including TIM19_TRGO , TIM19_CC3 , TIM19_CC4 , TIM2_CC2 , TIM3_TRGO , TIM4_CC4 , and EXTI_11 .

MS19995V2

Table 30. ADC pins

| Name | Signal type | Remarks |

|---|---|---|

| V REF+ | Input, analog reference positive | The higher/positive reference voltage for the ADC |

| V DDA (1) | Input, analog supply | Analog power supply equal to V DD |

| V REF- | Input, analog reference negative | The lower/negative reference voltage for the ADC, V REF- = V SSA |

| V SSA (1) | Input, analog supply ground | Ground for analog power supply equal to V SS |

| ADC_IN[15:0] | Analog signals | Up to 16 external analog channels plus three internal: V BAT , temperature sensor, and V REFINT (2) |

1. V DDA and V SSA have to be connected to V DD and V SS , respectively.

2. For full details about the ADC I/O pins, please refer to the “Pinouts and pin descriptions” section of the corresponding device datasheet.

12.3.1 ADC on-off control

The ADC can be powered-on by setting the ADON bit in the ADC_CR2 register. When the ADON bit is set for the first time, it wakes up the ADC from power-down mode.

Conversion starts when ADON bit is set for a second time by software after ADC power-up time (t STAB ).

You can stop conversion and put the ADC in power-down mode by resetting the ADON bit. In this mode the ADC consumes almost no power (only a few µA).

12.3.2 ADC clock

The ADCCLK clock provided by the Clock Controller is synchronous with the PCLK2 (APB2 clock). The RCC controller has a dedicated programmable prescaler for the ADC clock (refer to Section 6: Reset and clock control (RCC) for more details).

12.3.3 Channel selection

There are 16 multiplexed channels. It is possible to organize the conversions in two groups: regular and injected. A group consists of a sequence of conversions which can be done on any channel and in any order. For instance, it is possible to do the conversion in the following order: Ch3, Ch8, Ch2, Ch2, Ch0, Ch2, Ch2, Ch15.

- • The regular group is composed of up to 16 conversions. The regular channels and their order in the conversion sequence must be selected in the ADC_SQRx registers. The total number of conversions in the regular group must be written in the L[3:0] bits in the ADC_SQR1 register.

- • The injected group is composed of up to 4 conversions. The injected channels and their order in the conversion sequence must be selected in the ADC_JSQR register. The total number of conversions in the injected group must be written in the L[1:0] bits in the ADC_JSQR register.

If the ADC_SQRx or ADC_JSQR registers are modified during a conversion, the current conversion is reset and a new start pulse is sent to the ADC to convert the new chosen group.

Temperature sensor/ \( V_{REFINT}/V_{BAT} \) internal channels

The Temperature sensor is connected to channel ADC_IN16, the internal reference voltage \( V_{REFINT} \) is connected to ADC_IN17, and the \( V_{BAT} \) is connected to ADC_IN18. These internal channels can be selected and converted as injected or regular channels.

12.3.4 Single conversion mode

In single conversion mode the ADC does one conversion. This mode is started either by setting the ADON bit in the ADC_CR2 register (for a regular channel only) or by external trigger (for a regular or injected channel), while the CONT bit is 0.

Once the conversion of the selected channel is complete:

- • If a regular channel was converted:

- – The converted data is stored in the 16-bit ADC_DR register

- – The EOC (End Of Conversion) flag is set

- – and an interrupt is generated if the EOCIE is set.

- • If an injected channel was converted:

- – The converted data is stored in the 16-bit ADC_DRJ1 register

- – The JEOC (End Of Conversion Injected) flag is set

- – and an interrupt is generated if the JEOCIE bit is set.

The ADC is then stopped.

12.3.5 Continuous conversion mode

In continuous conversion mode ADC starts another conversion as soon as it finishes one. This mode is started either by external trigger or by setting the ADON bit in the ADC_CR2 register, while the CONT bit is 1.

After each conversion:

- • If a regular channel was converted:

- – The converted data is stored in the 16-bit ADC_DR register

- – The EOC (End Of Conversion) flag is set

- – An interrupt is generated if the EOCIE is set.

- • If an injected channel was converted:

- – The converted data is stored in the 16-bit ADC_DRJ1 register

- – The JEOC (End Of Conversion Injected) flag is set

- – An interrupt is generated if the JEOCIE bit is set.

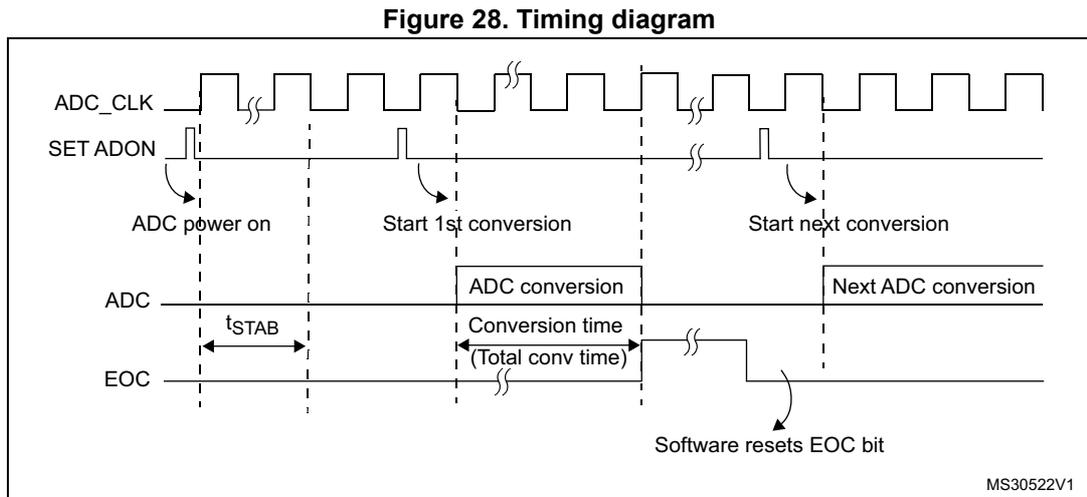

12.3.6 Timing diagram

As shown in Figure 28 , the ADC needs a stabilization time of \( t_{STAB} \) before it starts converting accurately. After the start of ADC conversion and after 14 clock cycles, the EOC flag is set and the 16-bit ADC Data register contains the result of the conversion.

Figure 28. Timing diagram

The diagram shows four signal lines over time.

ADC_CLK

is a periodic square wave.

SET ADON

is a signal that goes high to turn on the ADC and then low.

ADC

shows the conversion activity.

EOC

(End of Conversion) goes high when a conversion starts and low when it ends.

Key events:

1.

ADC power on

: Occurs when SET ADON goes high.

2.

t

STAB

: Stabilization time after power on.

3.

Start 1st conversion

: Occurs when SET ADON goes high again.

4.

ADC conversion

: The duration of the first conversion.

5.

Conversion time (Total conv time)

: The time from start to EOC going low.

6.

Start next conversion

: Occurs when SET ADON goes high a third time.

7.

Next ADC conversion

: The duration of the second conversion.

8.

Software resets EOC bit

: A manual reset of the EOC signal.

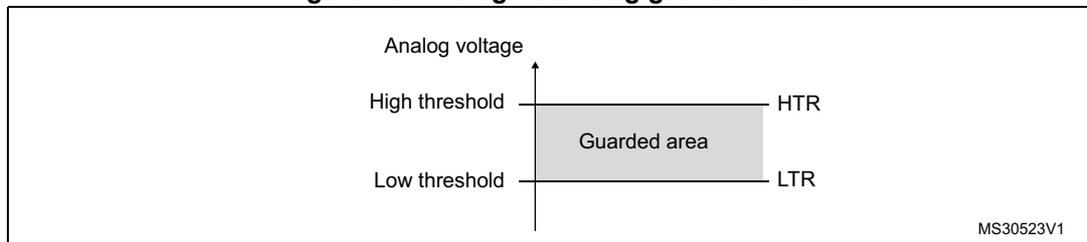

12.3.7 Analog watchdog

The AWD analog watchdog status bit is set if the analog voltage converted by the ADC is below a low threshold or above a high threshold. These thresholds are programmed in the 12 least significant bits of the ADC_HTR and ADC_LTR 16-bit registers. An interrupt can be enabled by using the AWDIE bit in the ADC_CR1 register.

The threshold value is independent of the alignment selected by the ALIGN bit in the ADC_CR2 register. The comparison is done before the alignment (see Section 12.5 ).

The analog watchdog can be enabled on one or more channels by configuring the ADC_CR1 register as shown in Table 31 .

Figure 29. Analog watchdog guarded area

The graph plots Analog voltage on the vertical axis. It shows two horizontal lines: High threshold (HTR) and Low threshold (LTR). The region between these two lines is shaded and labeled Guarded area . The HTR line is above the LTR line.

Table 31. Analog watchdog channel selection

| Channels to be guarded by analog watchdog | ADC_CR1 register control bits (x = don't care) | ||

|---|---|---|---|

| AWDSGL bit | AWDEN bit | JAWDEN bit | |

| None | x | 0 | 0 |

| All injected channels | 0 | 0 | 1 |

| All regular channels | 0 | 1 | 0 |

| All regular and injected channels | 0 | 1 | 1 |

| Single (1) injected channel | 1 | 0 | 1 |

| Single (1) regular channel | 1 | 1 | 0 |

| Single (1) regular or injected channel | 1 | 1 | 1 |

- 1. Selected by AWDCH[4:0] bits

12.3.8 Scan mode

This mode is used to scan a group of analog channels.

Scan mode can be selected by setting the SCAN bit in the ADC_CR1 register. Once this bit is set, ADC scans all the channels selected in the ADC_SQRx registers (for regular channels) or in the ADC_JSQR (for injected channels). A single conversion is performed for each channel of the group. After each end of conversion the next channel of the group is converted automatically. If the CONT bit is set, conversion does not stop at the last selected group channel but continues again from the first selected group channel.

When using scan mode, DMA bit must be set and the direct memory access controller is used to transfer the converted data of regular group channels to SRAM after each update of the ADC_DR register.

The injected channel converted data is always stored in the ADC_JDRx registers.

12.3.9 Injected channel management

Triggered injection

To use triggered injection, the JAUTO bit must be cleared and SCAN bit must be set in the ADC_CR1 register.

- 1. Start conversion of a group of regular channels either by external trigger or by setting the ADON bit in the ADC_CR2 register.

- 2. If an external injected trigger occurs during the regular group channel conversion, the current conversion is reset and the injected channel sequence is converted in scan once mode.

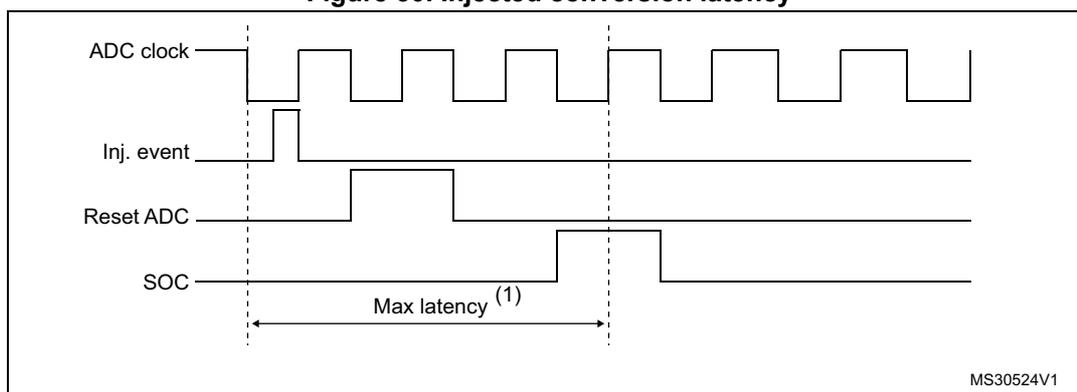

- 3. Then, the regular group channel conversion is resumed from the last interrupted regular conversion. If a regular event occurs during an injected conversion, it does not interrupt it but the regular sequence is executed at the end of the injected sequence. Figure 30 shows the timing diagram.

Note: When using triggered injection, one must ensure that the interval between trigger events is longer than the injection sequence. For instance, if the sequence length is 28 ADC clock cycles (that is two conversions with a 1.5 clock-period sampling time), the minimum interval between triggers must be 29 ADC clock cycles.

Auto-injection

If the JAUTO bit is set, then the injected group channels are automatically converted after the regular group channels. This can be used to convert a sequence of up to 20 conversions programmed in the ADC_SQRx and ADC_JSQR registers.

In this mode, external trigger on injected channels must be disabled.

If the CONT bit is also set in addition to the JAUTO bit, regular channels followed by injected channels are continuously converted.

For ADC clock prescalers ranging from 4 to 8, a delay of 1 ADC clock period is automatically inserted when switching from regular to injected sequence (respectively injected to regular). When the ADC clock prescaler is set to 2, the delay is 2 ADC clock periods.

Note: It is not possible to use both auto-injected and discontinuous modes simultaneously.

Figure 30. Injected conversion latency

1. The maximum latency value can be found in the electrical characteristics of the product datasheet.

12.3.10 Discontinuous mode

Regular group

This mode is enabled by setting the DISCEN bit in the ADC_CR1 register. It can be used to convert a short sequence of \( n \) conversions ( \( n \leq 8 \) ) which is a part of the sequence of conversions selected in the ADC_SQRx registers. The value of \( n \) is specified by writing to the DISCNUM[2:0] bits in the ADC_CR1 register.

When an external trigger occurs, it starts the next \( n \) conversions selected in the ADC_SQRx registers until all the conversions in the sequence are done. The total sequence length is defined by the L[3:0] bits in the ADC_SQR1 register.

Example:

\( n = 3 \) , channels to be converted = 0, 1, 2, 3, 6, 7, 9, 10

1st trigger: sequence converted 0, 1, 2; an EOC event is generated at each conversion

2nd trigger: sequence converted 3, 6, 7; an EOC event is generated at each conversion

3rd trigger: sequence converted 9, 10; an EOC event is generated at each conversion

4th trigger: sequence converted 0, 1, 2; an EOC event is generated at each conversion

Note: When a regular group is converted in discontinuous mode, no rollover will occur. When all sub groups are converted, the next trigger starts conversion of the first sub-group.

In the example above, the 4th trigger reconverts the 1st sub-group channels 0, 1 and 2.

Injected group

This mode is enabled by setting the JDISCEN bit in the ADC_CR1 register. It can be used to convert the sequence selected in the ADC_JSQR register, channel by channel, after an external trigger event.

When an external trigger occurs, it starts the next channel conversions selected in the ADC_JSQR registers until all the conversions in the sequence are done. The total sequence length is defined by the JL[1:0] bits in the ADC_JSQR register.

Example:

\( n = 1 \) , channels to be converted = 1, 2, 3

1st trigger: channel 1 converted

2nd trigger: channel 2 converted

3rd trigger: channel 3 converted and EOC and JEOC events generated

4th trigger: channel 1

Note: When all injected channels are converted, the next trigger starts the conversion of the first injected channel. In the example above, the 4th trigger reconverts the 1st injected channel 1.

It is not possible to use both auto-injected and discontinuous modes simultaneously.

The user must avoid setting discontinuous mode for both regular and injected groups together. Discontinuous mode must be enabled only for one group conversion.

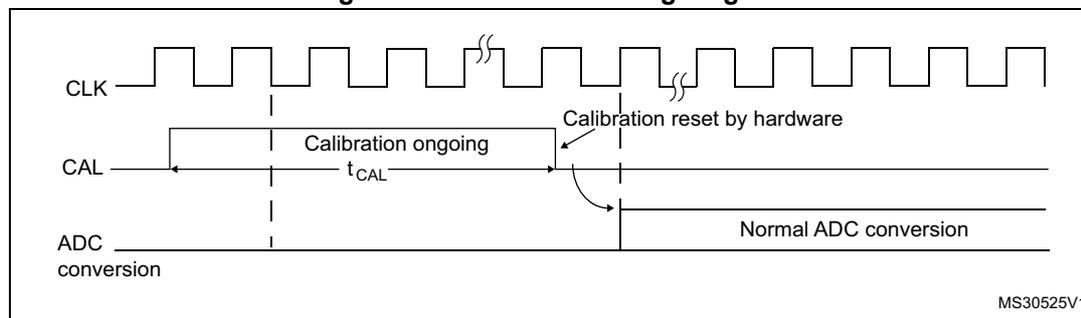

12.4 Calibration

The ADC has a built-in self calibration mode. Calibration significantly reduces accuracy errors due to internal capacitor bank variations. During calibration, an error-correction code (digital word) is calculated for each capacitor, and during all subsequent conversions, the error contribution of each capacitor is removed using this code.

Calibration is started by setting the CAL bit in the ADC_CR2 register. Once calibration is over, the CAL bit is reset by hardware and normal conversion can be performed. It is recommended to calibrate the ADC once at power-on. The calibration codes are stored in the ADC_DR as soon as the calibration phase ends.

Note: It is recommended to perform a calibration after each power-up.

Before starting a calibration the ADC must have been in power-on state (ADON bit = 1) for at least two ADC clock cycles.

Figure 31. Calibration timing diagram

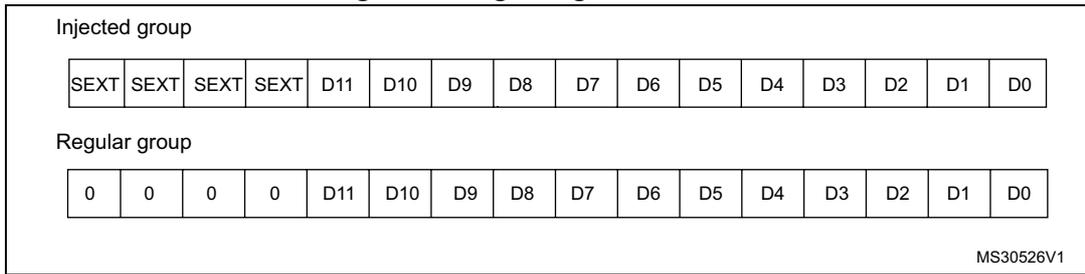

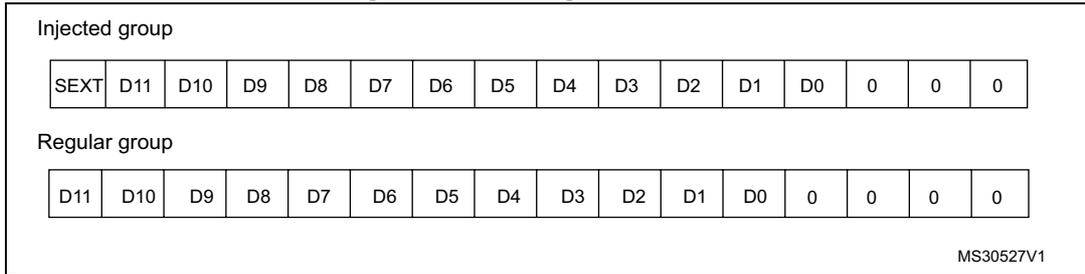

12.5 Data alignment

ALIGN bit in the ADC_CR2 register selects the alignment of data stored after conversion. Data can be left or right aligned as shown in Figure 32 and Figure 33 .

The injected group channels converted data value is decreased by the user-defined offset written in the ADC_JOFRx registers so the result can be a negative value. The SEXT bit is the extended sign value.

For regular group channels no offset is subtracted so only twelve bits are significant.

Figure 32. Right alignment of data

Injected group

| SEXT | SEXT | SEXT | SEXT | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

Regular group

| 0 | 0 | 0 | 0 | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

MS30526V1

Figure 33. Left alignment of data

Injected group

| SEXT | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | 0 | 0 | 0 |

Regular group

| D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | 0 | 0 | 0 | 0 |

MS30527V1

12.6 Channel-by-channel programmable sample time

ADC samples the input voltage for a number of ADC_CLK cycles which can be modified using the SMP[2:0] bits in the ADC_SMPR1 and ADC_SMPR2 registers. Each channel can be sampled with a different sample time.

The total conversion time is calculated as follows:

Example:

With an ADCCLK = 12 MHz and a sampling time of 1.5 cycles:

12.7 Conversion on external trigger

Conversion can be triggered by an external event (e.g. timer capture, EXTI line). If the EXTTRIG control bit is set then external events are able to trigger a conversion. The EXTSEL[2:0] and JEXTSEL[2:0] control bits allow the application to select decide which out of 8 possible events can trigger conversion for the regular and injected groups.

Note: When an external trigger is selected for ADC regular or injected conversion, only the rising edge of the signal can start the conversion.

Table 32. External trigger for regular channels for ADC1| Source | Type | EXTSEL[2:0] |

|---|---|---|

| TIM19_TRGO | Internal signal from on-chip timers | 000 |

| TIM19_CC3 | 001 | |

| TIM19_CC4 | 010 | |

| TIM2_CC2 event | 011 | |

| TIM3_TRGO event | 100 | |

| TIM4_CC4 event | 101 | |

| EXTI line 11 | External pin | 110 |

| SWSTART | Software control bit | 111 |

| Source | Connection type | JEXTSEL[2:0] |

|---|---|---|

| TIM19_CC1 | Internal signal from on-chip timers | 000 |

| TIM19_CC2 | 001 | |

| TIM2_TRGO event | 010 | |

| TIM2_CC1 event | 011 | |

| TIM3_CC4 event | 100 | |

| TIM4_TRGO event | 101 | |

| EXTI line 15 | External pin | 110 |

| JSWSTART | Software control bit | 111 |

The software source trigger events can be generated by setting a bit in a register (SWSTART and JSWSTART in ADC_CR2).

A regular group conversion can be interrupted by an injected trigger.

12.8 DMA request

Since converted regular channels value are stored in a unique data register, it is necessary to use DMA for conversion of more than one regular channel. This avoids the loss of data already stored in the ADC_DR register.

Only the end of conversion of a regular channel generates a DMA request, which allows the transfer of its converted data from the ADC_DR register to the destination location selected by the user.

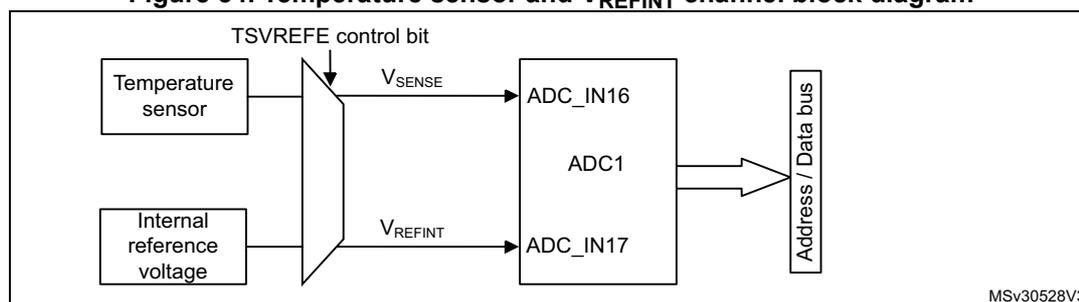

12.9 Temperature sensor and internal reference voltage

The temperature sensor can be used to measure the ambient temperature ( \( T_A \) ) of the device. The temperature sensor is internally connected to the ADC_IN16 input channel

which is used to convert the sensor output voltage into a digital value. The recommended sampling time for the temperature sensor is 17.1 \( \mu\text{s} \) .

The internal voltage reference ( \( V_{\text{REFINT}} \) ) provides a stable (bandgap) voltage output for the ADC and Comparators. \( V_{\text{REFINT}} \) is internally connected to the ADC_IN17 input channel. The precise voltage of \( V_{\text{REFINT}} \) is individually measured for each part by ST during production test and stored in the system memory area. It is accessible in read-only mode.

Figure 34 shows the block diagram of the temperature sensor.

When not in use, this sensor can be put in power-down mode.

Note: The TSVREFE bit must be set to enable both internal channels: ADC_IN16 (temperature sensor) and ADC_IN17 ( \( V_{\text{REFINT}} \) ) conversion.

The temperature sensor output voltage changes linearly with temperature. The offset of this line varies from chip to chip due to process variation (up to 45 °C from one chip to another).

The internal temperature sensor is more suited for applications that detect temperature variations instead of absolute temperatures. If accurate temperature readings are needed, an external temperature sensor part should be used.

During the manufacturing process, the calibration data of the temperature sensor and the internal voltage reference are stored in the system memory area. The user application can then read them and use them to improve the accuracy of the temperature sensor or the internal reference. Refer to the datasheet for additional information.

Figure 34. Temperature sensor and \( V_{\text{REFINT}} \) channel block diagram

graph LR

subgraph Internal

TS[Temperature sensor] -- V_SENSE --> ADC1

IRV[Internal reference voltage] -- V_REFINT --> ADC1

TSVREFE[TSVREFE control bit] --> MUX

MUX --> ADC1

end

ADC1[ADC1] --> Bus[Address / Data bus]Reading the temperature

To use the sensor:

- 1. Select the ADC_IN16 input channel.

- 2. Select a sample time of 17.1 \( \mu\text{s} \)

- 3. Set the TSVREFE bit in the ADC control register 2 (ADC_CR2) to wake up the temperature sensor from power-down mode.

- 4. Start the ADC conversion by setting the ADON bit (or by external trigger).

- 5. Read the resulting \( V_{\text{SENSE}} \) data in the ADC data register

- 6. Obtain the temperature using the following formula:\[ \text{Temperature (in } ^\circ\text{C)} = \{(V_{25} - V_{\text{SENSE}}) / \text{Avg\_Slope}\} + 25. \]Where,

\( V_{25} = V_{\text{SENSE}} \) value for \( 25^\circ\text{C} \) and

\( \text{Avg\_Slope} = \text{Average Slope for curve between Temperature vs. } V_{\text{SENSE}} \) (given in \( \text{mV}/^\circ\text{C} \) or \( \mu\text{V}/^\circ\text{C} \) ).

Refer to the Electrical characteristics section for the actual values of \( V_{25} \) and \( \text{Avg\_Slope} \) .

Note: The sensor has a startup time after waking from power-down mode before it can output \( V_{\text{SENSE}} \) at the correct level. The ADC also has a startup time after power-on, so to minimize the delay, the ADON and TSVREFE bits should be set at the same time.

12.10 Battery voltage monitoring

The VBAT_MON bit in the SYSCFG_CFGR1 register allows the backup battery voltage on the VBAT pin to be measured.

As the VBAT voltage can be higher than VDDA, to ensure the correct operation of the ADC, the VBAT pin is internally connected to a bridge divider by 2. This bridge is automatically enabled when VBAT_MON is set, to connect VBAT/2 to the ADC1_IN18 input channel. Consequently, the converted digital value is half the VBAT voltage. To prevent any unwanted consumption on the battery, it is recommended to enable the bridge divider only when needed, for ADC conversion.

12.11 ADC interrupts

An interrupt can be produced on end of conversion for regular and injected groups and when the analog watchdog status bit is set. Separate interrupt enable bits are available for flexibility.

Two other flags are present in the ADC_SR register, but there is no interrupt associated with them:

- • JSTRT (Start of conversion for injected group channels)

- • STRT (Start of conversion for regular group channels)

Table 34. ADC interrupts

| Interrupt event | Event flag | Enable Control bit |

|---|---|---|

| End of conversion regular group | EOC | EOCIE |

| End of conversion injected group | JEOC | JEOCIE |

| Analog watchdog status bit is set | AWD | AWDIE |

12.12 ADC registers

Refer to Section 1.2 on page 36 for a list of abbreviations used in register descriptions.

The peripheral registers have to be accessed by words (32-bit).

12.12.1 ADC status register (ADC_SR)

Address offset: 0x00

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | |||||||||||||||

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | STRT | JSTRT | JEEOC | EOC | AWD |

| rc_w0 | rc_w0 | rc_w0 | rc_w0 | rc_w0 | |||||||||||

Bits 31:5 Reserved, must be kept at reset value.

Bit 4 STRT : Regular channel Start flag

This bit is set by hardware when regular channel conversion starts. It is cleared by software.

0: No regular channel conversion started

1: Regular channel conversion has started

Bit 3 JSTRT : Injected channel Start flag

This bit is set by hardware when injected channel group conversion starts. It is cleared by software.

0: No injected group conversion started

1: Injected group conversion has started

Bit 2 JEEOC : Injected channel end of conversion

This bit is set by hardware at the end of all injected group channel conversion. It is cleared by software.

0: Conversion is not complete

1: Conversion complete

Bit 1 EOC : End of conversion

This bit is set by hardware at the end of a group channel conversion (regular or injected). It is cleared by software or by reading the ADC_DR.

0: Conversion is not complete

1: Conversion complete

Bit 0 AWD : Analog watchdog flag

This bit is set by hardware when the converted voltage crosses the values programmed in the ADC_LTR and ADC_HTR registers. It is cleared by software.

0: No Analog watchdog event occurred

1: Analog watchdog event occurred

12.12.2 ADC control register 1 (ADC_CR1)

Address offset: 0x04

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | AWDEN | JAWDEN | Res. | Res. | Res. | Res. | Res. | Res. |

| rw | rw | ||||||||||||||

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| DISCNUM[2:0] | JDISCEN | DISCEN | JAUTO | AWDSGL | SCAN | JEOCIE | AWDIE | EOCIE | AWDCH[4:0] | ||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:24 Reserved, must be kept at reset value.

Bit 23 AWDEN : Analog watchdog enable on regular channels

This bit is set/reset by software.

0: Analog watchdog disabled on regular channels

1: Analog watchdog enabled on regular channels

Bit 22 JAWDEN : Analog watchdog enable on injected channels

This bit is set/reset by software.

0: Analog watchdog disabled on injected channels

1: Analog watchdog enabled on injected channels

Bits 21:16 Reserved, must be kept at reset value.

Bits 15:13 DISCNUM[2:0] : Discontinuous mode channel count

These bits are written by software to define the number of regular channels to be converted in discontinuous mode, after receiving an external trigger.

000: 1 channel

001: 2 channels

.....

111: 8 channels

Bit 12 JDISCEN : Discontinuous mode on injected channels

This bit set and cleared by software to enable/disable discontinuous mode on injected group channels

0: Discontinuous mode on injected channels disabled

1: Discontinuous mode on injected channels enabled

Bit 11 DISCEN : Discontinuous mode on regular channels

This bit set and cleared by software to enable/disable discontinuous mode on regular channels.

0: Discontinuous mode on regular channels disabled

1: Discontinuous mode on regular channels enabled

Bit 10 JAUTO : Automatic Injected Group conversion

This bit set and cleared by software to enable/disable automatic injected group conversion after regular group conversion.

0: Automatic injected group conversion disabled

1: Automatic injected group conversion enabled

Bit 9 AWDSGL : Enable the watchdog on a single channel in scan mode

This bit set and cleared by software to enable/disable the analog watchdog on the channel identified by the AWDCH[4:0] bits.

0: Analog watchdog enabled on all channels

1: Analog watchdog enabled on a single channel

Bit 8 SCAN : Scan mode

This bit is set and cleared by software to enable/disable scan mode. In scan mode, the inputs selected through the ADC_SQRx or ADC_JSQRx registers are converted.

0: Scan mode disabled

1: Scan mode enabled

Note: An EOC or JEOC interrupt is generated only on the end of conversion of the last channel if the corresponding EOCIE or JEOCIE bit is set

Bit 7 JEOCIE : Interrupt enable for injected channels

This bit is set and cleared by software to enable/disable the end of conversion interrupt for injected channels.

0: JEOC interrupt disabled

1: JEOC interrupt enabled. An interrupt is generated when the JEOC bit is set.

Bit 6 AWDIE : Analog watchdog interrupt enable

This bit is set and cleared by software to enable/disable the analog watchdog interrupt.

0: Analog watchdog interrupt disabled

1: Analog watchdog interrupt enabled

Bit 5 EOCIE : Interrupt enable for EOC

This bit is set and cleared by software to enable/disable the End of Conversion interrupt.

0: EOC interrupt disabled

1: EOC interrupt enabled. An interrupt is generated when the EOC bit is set.

Bits 4:0 AWDCH[4:0] : Analog watchdog channel select bits

These bits are set and cleared by software. They select the input channel to be guarded by the Analog watchdog.

00000: ADC analog Channel0

00001: ADC analog Channel1

...

01111: ADC analog Channel15

10000: ADC analog Channel16

10001: ADC analog Channel17

10010: ADC analog Channel18

Other values reserved.

Note: ADC1 analog Channel16, Channel17 and Channel 18 are internally connected to the temperature sensor, to V REFINT and to V BAT /2 respectively.

12.12.3 ADC control register 2 (ADC_CR2)

Address offset: 0x08

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | TSVREFE | SWSTART | JSWSTART | EXTTRIG | EXTSEL[2:0] | Res. | ||

| rw | rw | rw | rw | rw | rw | rw | |||||||||

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| JEXTTRIG | JEXTSEL[2:0] | ALIGN | Res. | Res. | DMA | Res. | Res. | Res. | Res. | RSTCAL | CAL | CONT | ADON | ||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | ||||||

Bits 31:24 Reserved, must be kept at reset value.

Bit 23 TSVREFE : Temperature sensor and \( V_{REFINT} \) enable

This bit is set and cleared by software to enable/disable the temperature sensor and

\(

V_{REFINT}

\)

channel.

0: Temperature sensor and

\(

V_{REFINT}

\)

channel disabled

1: Temperature sensor and

\(

V_{REFINT}

\)

channel enabled

Bit 22 SWSTART : Start conversion of regular channels

This bit is set by software to start conversion and cleared by hardware as soon as conversion starts. It starts a conversion of a group of regular channels if SWSTART is selected as trigger event by the EXTSEL[2:0] bits.

0: Reset state

1: Starts conversion of regular channels

Bit 21 JSWSTART : Start conversion of injected channels

This bit is set by software and cleared by software or by hardware as soon as the conversion starts. It starts a conversion of a group of injected channels (if JSWSTART is selected as trigger event by the JEXTSEL[2:0] bits).

0: Reset state

1: Starts conversion of injected channels

Bit 20 EXTTRIG : External trigger conversion mode for regular channels

This bit is set and cleared by software to enable/disable the external trigger used to start conversion of a regular channel group.

0: Conversion on external event disabled

1: Conversion on external event enabled

Bits 19:17 EXTSEL[2:0] : External event select for regular group

These bits select the external event used to trigger the start of conversion of a regular group:

- 000: Timer 19 TRGO event

- 001: Timer 19 CC3 event

- 010: Timer 19 CC4 event

- 011: Timer 2 CC2 event

- 100: Timer 3 TRGO event

- 101: Timer 4 CC4 event

- 110: EXTI line 11

- 111: SWSTART

Bit 16 Reserved, must be kept at reset value.

Bit 15 JEXTTRIG : External trigger conversion mode for injected channels

This bit is set and cleared by software to enable/disable the external trigger used to start conversion of an injected channel group.

0: Conversion on external event disabled

1: Conversion on external event enabled

Bits 14:12 JEXTSEL[2:0] : External event select for injected group

These bits select the external event used to trigger the start of conversion of an injected group:

000: Timer 19 CC1 event

001: Timer 19 CC2 event

010: Timer 2 TRGO event

011: Timer 2 CC1 event

100: Timer 3 CC4 event

101: Timer 4 TRGO event

110: EXTI line15

111: JSWSTART

Bit 11 ALIGN : Data alignment

This bit is set and cleared by software. Refer to Figure 32 and Figure 33 .

0: Right Alignment

1: Left Alignment

Bits 10:9 Reserved, must be kept at reset value.

Bit 8 DMA : Direct memory access mode

This bit is set and cleared by software. Refer to the DMA controller chapter for more details.

0: DMA mode disabled

1: DMA mode enabled

Bits 7:4 Reserved, must be kept at reset value.

Bit 3 RSTCAL : Reset calibration

This bit is set by software and cleared by hardware. It is cleared after the calibration registers are initialized.

0: Calibration register initialized.

1: Initialize calibration register.

Note: If RSTCAL is set when conversion is ongoing, additional cycles are required to clear the calibration registers.

Bit 2 CAL : A/D Calibration

This bit is set by software to start the calibration. It is reset by hardware after calibration is complete.

0: Calibration completed

1: Enable calibration

Bit 1 CONT : Continuous conversion

This bit is set and cleared by software. If set conversion takes place continuously till this bit is reset.

0: Single conversion mode

1: Continuous conversion mode

Bit 0 ADON : A/D converter ON / OFF

This bit is set and cleared by software. If this bit holds a value of zero and a 1 is written to it then it wakes up the ADC from power-down state.

Conversion starts when this bit holds a value of 1 and a 1 is written to it. The application should allow a delay of \( t_{STAB} \) between power up and start of conversion. Refer to Figure 28 .

0: Disable ADC conversion/calibration and go to power-down mode.

1: Enable ADC and to start conversion

Note: If any other bit in this register apart from ADON is changed at the same time, then conversion is not triggered. This is to prevent triggering an erroneous conversion.

12.12.4 ADC sample time register 1 (ADC_SMPR1)

Address offset: 0x0C

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 25 24 | 23 22 21 | 20 19 18 | 17 16 | |||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | Res. | Res. | Res. | Res. | SMP18[2:0] | SMP17[2:0] | SMP16[2:0] | SMP15[2:1] | |||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | |||||

| 15 | 14 13 12 | 11 10 9 | 8 7 6 | 5 4 3 | 2 1 0 | ||||||||||

| SMP15[0] | SMP14[2:0] | SMP13[2:0] | SMP12[2:0] | SMP11[2:0] | SMP10[2:0] | ||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:27 Reserved, must be kept at reset value.

Bits 26:0 SMPx[2:0] : Channel x Sample time selection

These bits are written by software to select the sample time individually for each channel. During sample cycles channel selection bits must remain unchanged.

- 000: 1.5 cycles

- 001: 7.5 cycles

- 010: 13.5 cycles

- 011: 28.5 cycles

- 100: 41.5 cycles

- 101: 55.5 cycles

- 110: 71.5 cycles

- 111: 239.5 cycles

ADC1 analog Channel16, Channel 17 and Channel18 are internally connected to the temperature sensor, to \( V_{REFINT} \) and to \( V_{BAT}/2 \) respectively.

12.12.5 ADC sample time register 2 (ADC_SMPR2)

Address offset: 0x10

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | Res. | SMP9[2:0] | SMP8[2:0] | SMP7[2:0] | SMP6[2:0] | SMP5[2:1] | |||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | ||

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SMP5[0] | SMP4[2:0] | SMP3[2:0] | SMP2[2:0] | SMP1[2:0] | SMP0[2:0] | ||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:30 Reserved, must be kept at reset value.

Bits 29:0 SMPx[2:0] : Channel x Sample time selection

These bits are written by software to select the sample time individually for each channel. During sample cycles channel selection bits must remain unchanged.

000: 1.5 cycles

001: 7.5 cycles

010: 13.5 cycles

011: 28.5 cycles

100: 41.5 cycles

101: 55.5 cycles

110: 71.5 cycles

111: 239.5 cycles

12.12.6 ADC injected channel data offset register x (ADC_JOFRx) (x=1..4)

Address offset: 0x14-0x20

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Res. | Res. | Res. | Res. | JOFFSETx[11:0] | |||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | ||||

Bits 31:12 Reserved, must be kept at reset value.

Bits 11:0 JOFFSETx[11:0] : Data offset for injected channel x

These bits are written by software to define the offset to be subtracted from the raw converted data when converting injected channels. The conversion result can be read from in the ADC_JDRx registers.

12.12.7 ADC watchdog high threshold register (ADC_HTR)

Address offset: 0x24

Reset value: 0x0000 0FFF

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Res. | Res. | Res. | Res. | HT[11:0] | |||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | ||||

Bits 31:12 Reserved, must be kept at reset value.

Bits 11:0 HT[11:0] : Analog watchdog high threshold

These bits are written by software to define the high threshold for the analog watchdog.

Note: This register can be written by software when the ADC conversion is ongoing. The programmed value is effective from the next EOC when the watchdog comparison is happened. When the software writes this register, due to the write delay on the register, it can create uncertainty on the effective timing of the new programmed value.

12.12.8 ADC watchdog low threshold register (ADC_LTR)

Address offset: 0x28

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Res. | Res. | Res. | Res. | LT[11:0] | |||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | ||||

Bits 31:12 Reserved, must be kept at reset value.

Bits 11:0 LT[11:0] : Analog watchdog low threshold

These bits are written by software to define the low threshold for the analog watchdog.

Note: This register can be written by software when the ADC conversion is ongoing. The programmed value is effective from the next EOC when the watchdog comparison is happened. When the software writes this register, due to the write delay on the register, it can create uncertainty on the effective timing of the new programmed value.

12.12.9 ADC regular sequence register 1 (ADC_SQR1)

Address offset: 0x2C

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | L[3:0] | SQ16[4:1] | ||||||

| rw | rw | rw | rw | rw | rw | rw | rw | ||||||||

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SQ16[0] | SQ15[4:0] | SQ14[4:0] | SQ13[4:0] | ||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:24 Reserved, must be kept at reset value.

Bits 23:20 L[3:0] : Regular channel sequence length

These bits are written by software to define the total number of conversions in the regular channel conversion sequence.

0000: 1 conversion

0001: 2 conversions

.....

1111: 16 conversions

Bits 19:15 SQ16[4:0] : 16th conversion in regular sequence

These bits are written by software with the channel number (0..18) assigned as the 16th in the conversion sequence.

Bits 14:10 SQ15[4:0] : 15th conversion in regular sequence

Bits 9:5 SQ14[4:0] : 14th conversion in regular sequence

Bits 4:0 SQ13[4:0] : 13th conversion in regular sequence

12.12.10 ADC regular sequence register 2 (ADC_SQR2)

Address offset: 0x30

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | Res. | SQ12[4:0] | SQ11[4:0] | SQ10[4:1] | |||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | ||

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SQ10[0] | SQ9[4:0] | SQ8[4:0] | SQ7[4:0] | ||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:30 Reserved, must be kept at reset value.

Bits 29:26 SQ12[4:0] : 12th conversion in regular sequence

These bits are written by software with the channel number (0..18) assigned as the 12th in the sequence to be converted.

Bits 24:20 SQ11[4:0] : 11th conversion in regular sequence

Bits 19:15 SQ10[4:0] : 10th conversion in regular sequence

Bits 14:10 SQ9[4:0] : 9th conversion in regular sequence

Bits 9:5 SQ8[4:0] : 8th conversion in regular sequence

Bits 4:0 SQ7[4:0] : 7th conversion in regular sequence

12.12.11 ADC regular sequence register 3 (ADC_SQR3)

Address offset: 0x34

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | Res. | SQ6[4:0] | SQ5[4:0] | SQ4[4:1] | |||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | ||

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SQ4[0] | SQ3[4:0] | SQ2[4:0] | SQ1[4:0] | ||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:30 Reserved, must be kept at reset value.

Bits 29:25 SQ6[4:0] : 6th conversion in regular sequence

These bits are written by software with the channel number (0..18) assigned as the 6th in the sequence to be converted.

Bits 24:20 SQ5[4:0] : 5th conversion in regular sequence

Bits 19:15 SQ4[4:0] : 4th conversion in regular sequence

Bits 14:10 SQ3[4:0] : 3rd conversion in regular sequence

Bits 9:5 SQ2[4:0] : 2nd conversion in regular sequence

Bits 4:0 SQ1[4:0] : 1st conversion in regular sequence

12.12.12 ADC injected sequence register (ADC_JSQR)

Address offset: 0x38

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | JL[1:0] | JSQ4[4:1] | ||||

| rw | rw | rw | rw | rw | rw | ||||||||||

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| JSQ4[0] | JSQ3[4:0] | JSQ2[4:0] | JSQ1[4:0] | ||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:22 Reserved, must be kept at reset value.

Bits 21:20 JL[1:0] : Injected sequence length

These bits are written by software to define the total number of conversions in the injected channel conversion sequence.

00: 1 conversion

01: 2 conversions

10: 3 conversions

11: 4 conversions

Bits 19:15 JSQ4[4:0] : 4th conversion in injected sequence (when JL[1:0] = 3) (1)

These bits are written by software with the channel number (0..18) assigned as the 4th in the sequence to be converted.

Note: Unlike a regular conversion sequence, if JL[1:0] length is less than four, the channels are converted in a sequence starting from (4-JL). Example: ADC_JSQR[21:0] = 10 00011 00011 00111 00010 means that a scan conversion will convert the following channel sequence: 7, 3, 3, 3. (not 2, 7, 3)

Bits 14:10 JSQ3[4:0] : 3rd conversion in injected sequence (when JL[1:0] = 3)

Bits 9:5 JSQ2[4:0] : 2nd conversion in injected sequence (when JL[1:0] = 3)

Bits 4:0 JSQ1[4:0] : 1st conversion in injected sequence (when JL[1:0] = 3)

- When JL=3 (4 injected conversions in the sequencer), the ADC converts the channels in this order:

JSQ1[4:0] >> JSQ2[4:0] >> JSQ3[4:0] >> JSQ4[4:0]

When JL=2 (3 injected conversions in the sequencer), the ADC converts the channels in this order:

JSQ2[4:0] >> JSQ3[4:0] >> JSQ4[4:0]

When JL=1 (2 injected conversions in the sequencer), the ADC converts the channels in this order:

JSQ3[4:0] >> JSQ4[4:0]

When JL=0 (1 injected conversion in the sequencer), the ADC converts only JSQ4[4:0] channel

12.12.13 ADC injected data register x (ADC_JDRx) (x= 1..4)

Address offset: 0x3C - 0x48

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| JDATA[15:0] | |||||||||||||||

| r | r | r | r | r | r | r | r | r | r | r | r | r | r | r | r |

Bits 31:16 Reserved, must be kept at reset value.

Bits 15:0 JDATA[15:0] : Injected data

These bits are read only. They contain the conversion result from injected channel x. The data is left or right-aligned as shown in Figure 32 and Figure 33 .

12.12.14 ADC regular data register (ADC_DR)

Address offset: 0x4C

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| DATA[15:0] | |||||||||||||||

| r | r | r | r | r | r | r | r | r | r | r | r | r | r | r | r |

Bits 31:16 Reserved, must be kept at reset value.

Bits 15:0 DATA[15:0] : Regular data

These bits are read only. They contain the conversion result from the regular channels. The data is left or right-aligned as shown in Figure 32 and Figure 33 .

12.13 ADC register map

The following table summarizes the ADC registers.

Table 35. ADC register map and reset values

| Offset | Register | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 0x00 | ADC_SR | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | STR | JS | EOC | AWD |

| Reset value | 0 | 0 | 0 | 0 | 0 |

| Offset | Register | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 0x04 | ADC_CR1 | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | AWDEN | JAWDEN | Res. | Res. | Res. | Res. | Res. | Res. | DISC NUM [2:0] | JDISCEN | DISCEN | JAUTO | AWD SGL | SCAN | JEOC IE | AWDIE | EOCIE | AWDCH[4:0] | |||||||

| Reset value | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | ||||||||||||||||

| 0x08 | ADC_CR2 | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | TSVREFE | SWSTART | JSWSTART | EXTTRIG | EXTSEL [2:0] | Res. | JEXTTRIG | JEXTSE L[2:0] | ALIGN | Res. | Res. | DMA | Res. | Res. | Res. | Res. | Res. | RSTCAL | CAL | CONT | ADON | ||||

| Reset value | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |||||||||||||||||

| 0x0C | ADC_SMPR1 | Sample time bits SMPx_x | ||||||||||||||||||||||||||||||||

| Reset value | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | ||

| 0x10 | ADC_SMPR2 | Sample time bits SMPx_x | ||||||||||||||||||||||||||||||||

| Reset value | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | ||

| 0x14 | ADC_JOFR1 | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | JOFFSET1[11:0] | ||||||||||||

| Reset value | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | ||||||||||||||||||||||

| 0x18 | ADC_JOFR2 | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | JOFFSET2[11:0] | ||||||||||||

| Reset value | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | ||||||||||||||||||||||

| 0x1C | ADC_JOFR3 | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | JOFFSET3[11:0] | ||||||||||||

| Reset value | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | ||||||||||||||||||||||

| 0x20 | ADC_JOFR4 | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | JOFFSET4[11:0] | ||||||||||||

| Reset value | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | ||||||||||||||||||||||

| 0x24 | ADC_HTR | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | HT[11:0] | ||||||||||||

| Reset value | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | ||||||||||||||||||||||

| 0x28 | ADC_LTR | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | LT[11:0] | ||||||||||||

| Reset value | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | ||||||||||||||||||||||

| 0x2C | ADC_SQR1 | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | L[3:0] | SQ16[4:0] | SQ15[4:0] | SQ14[4:0] | SQ13[4:0] | ||||||||||||||||||||

| Reset value | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | ||||||||||

| 0x30 | ADC_SQR2 | Res. | Res. | SQ12[4:0] | SQ11[4:0] | SQ10[4:0] | SQ9[4:0] | SQ8[4:0] | SQ7[4:0] | |||||||||||||||||||||||||

| Reset value | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | ||||

| 0x34 | ADC_SQR3 | Res. | Res. | SQ6[4:0] | SQ5[4:0] | SQ4[4:0] | SQ3[4:0] | SQ2[4:0] | SQ1[4:0] | |||||||||||||||||||||||||

| Reset value | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | ||||

Table 35. ADC register map and reset values (continued)

| Offset | Register | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 0x38 | ADC_JSQR | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | JL[1:0] | JSQ4[4:0] | JSQ3[4:0] | JSQ2[4:0] | JSQ1[4:0] | |||||||||||||||||

| Reset value | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |||||||||||

| 0x3C | ADC_JDR1 | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | JDATA[15:0] | |||||||||||||||

| Reset value | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | ||||||||||||||||||

| 0x40 | ADC_JDR2 | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | JDATA[15:0] | |||||||||||||||

| Reset value | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | ||||||||||||||||||

| 0x44 | ADC_JDR3 | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | JDATA[15:0] | |||||||||||||||

| Reset value | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | ||||||||||||||||||

| 0x48 | ADC_JDR4 | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | JDATA[15:0] | |||||||||||||||

| Reset value | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | ||||||||||||||||||

| 0x4C | ADC_DR | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Regular DATA[15:0] | |||||||||||||||

| Reset value | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | ||||||||||||||||||

Refer to Section 2.2 on page 40 for the register boundary addresses.